# Heterogeneous integration of InAs/GaSb tunnel diode structure on silicon using 200 nm GaAsSb dislocation filtering buffer

J.-S. Liu, M. Clavel, R. Pandey, S. Datta, Y. Xie, J. J. Heremans, and M. K. Hudait

Citation: AIP Advances 8, 105108 (2018); doi: 10.1063/1.5042064

View online: https://doi.org/10.1063/1.5042064

View Table of Contents: http://aip.scitation.org/toc/adv/8/10

Published by the American Institute of Physics

# Articles you may be interested in

Growth and characterization of metamorphic InAs/GaSb tunnel heterojunction on GaAs by molecular beam epitaxy

Journal of Applied Physics 119, 244308 (2016); 10.1063/1.4954794

InAs/GaSb type-II superlattice infrared detectors: Future prospect

Applied Physics Reviews 4, 031304 (2017); 10.1063/1.4999077

Significantly extended cutoff wavelength of very long-wave infrared detectors based on InAs/GaSb/InSb/GaSb superlattices

Applied Physics Letters 111, 161101 (2017); 10.1063/1.4998502

Minority carrier diffusion length for electrons in an extended SWIR InAs/AISb type-II superlattice photodiode Applied Physics Letters **111**, 201106 (2017); 10.1063/1.5005097

Atomistic modeling trap-assisted tunneling in hole tunnel field effect transistors

Journal of Applied Physics 123, 174504 (2018); 10.1063/1.5018737

Integration of broken-gap heterojunction InAs/GaSb Esaki tunnel diodes on silicon

Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena **33**, 062203 (2015); 10.1116/1.4935885

Don't let your writing keep you from getting published!

Learn more today!

# Heterogeneous integration of InAs/GaSb tunnel diode structure on silicon using 200 nm GaAsSb dislocation filtering buffer

J.-S. Liu,<sup>1</sup> M. Clavel,<sup>1</sup> R. Pandey,<sup>2</sup> S. Datta,<sup>3</sup> Y. Xie,<sup>4</sup> J. J. Heremans,<sup>4</sup> and M. K. Hudait<sup>1,a</sup>

(Received 29 May 2018; accepted 28 September 2018; published online 8 October 2018)

An InAs/GaSb tunnel diode structure was heterogeneously integrated on silicon by solid source molecular beam epitaxy using a 200 nm strained GaAs<sub>1-v</sub>Sb<sub>v</sub> dislocation filtering buffer. X-ray analysis demonstrated near complete strain relaxation of the metamorphic buffer and a quasi-lattice-matched InAs/GaSb heterostructure, while high-resolution transmission electron microscopy revealed sharp, atomically abrupt heterointerfaces between the GaSb and InAs epilayers. In-plane magnetotransport analysis revealed Shubnikov-de Haas oscillations, indicating the presence of a dominant high mobility carrier, thereby testifying to the quality of the heterostructure and interfaces. Temperature-dependent current-voltage characteristics of fabricated InAs/GaSb tunnel diodes demonstrated Shockley-Read-Hall generation-recombination at low bias and band-to-band tunneling transport at high bias. The extracted conductance slope from the fabricated tunnel diodes increased with increasing temperature due to thermal emission ( $E_a \sim 0.48 \text{ eV}$ ) and trapassisted tunneling. Thus, this work illustrates the significance of defect control in the heterointegration of metamorphic InAs/GaSb tunnel diode heterostructures on silicon when using  $GaAs_{1-y}Sb_y$  dislocation filtering buffers. © 2018 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/). https://doi.org/10.1063/1.5042064

# I. INTRODUCTION

Tunneling field-effect transistors (TFETs) have been extensively studied  $^{1-20}$  for their application to low-power digital logic due to their (i) steep subthreshold-swing (SS) characteristics, (ii) high drive current ( $I_{ON}$ ), (iii) low threshold voltage ( $V_{TH}$ ), and (iv) high ON-state to OFF-state current ratio ( $I_{ON}/I_{OFF}$ ). One enticing approach towards the realization of TFET devices is the adoption of heterogeneous material systems (e.g.,  $I_{I_X}Ga_{1-X}As/GaAs_{1-Y}Sb_y$ ), thereby allowing device designers to tailor the effective tunneling barrier height ( $E_{beff}$ ) via alloy composition.  $^{11,12,21-23}$  Although mixed arsenide/antimonide-based TFET architectures have shown progress in realizing step SS (<60 mV/dec) $^{10,20}$  and low  $E_{beff}$  (<0.5 V) operation, they have been limited to smaller diameter, cost-prohibitive III-V substrates. Therefore, the heterogeneous integration of a mixed As/Sb material system (e.g., broken-gap InAs/GaSb) on Si would be a significant step towards the integration of III-V TFETs into the Si CMOS process flow. However, the heterogeneous integration of mixed As/Sb device structures faces several challenges due to differences in material properties, including:

<sup>&</sup>lt;sup>1</sup>Electrical and Computer Engineering, Virginia Tech, Blacksburg, Virginia 24061, USA <sup>2</sup>Electrical Engineering, The Pennsylvania State University, University Park, Pennsylvania 16802, USA

<sup>&</sup>lt;sup>3</sup>Electrical Engineering, University of Notre Dame, Notre Dame, Indiana 46556, USA <sup>4</sup>Department of Physics, Virginia Tech, Blacksburg, Virginia 24061, USA

<sup>&</sup>lt;sup>a</sup>Contact author: Tel: (540) 231-6663, Fax: (540) 231-3362, E-mail: mantu.hudait@vt.edu

(i) thermal expansion coefficient mismatch-induced stress;<sup>24</sup> (ii) anti-phase domain formation due to polar (III-V) on non-polar (Si) heteroepitaxy; and (iii) lattice mismatch-induced crystal defects and dislocations.<sup>25–28</sup>

Several approaches have been implemented to address these challenges, such as metamorphic buffer architectures, <sup>25–32</sup> strained-layer superlattice buffers, <sup>25,33</sup> migration enhanced epitaxy utilizing off-cut substrates, <sup>34–38</sup> combined low- and high-temperature growth phases interspersed with thermal cycling annealing, <sup>39–48</sup> and the intentional formation of interfacial misfit dislocation (IMF) arrays at the substrate/buffer heterointerface. 49,50 Specific to InAs/GaSb-based tunnel FET structures on Si, Bhatnagar et al.<sup>51</sup> employed off-cut Si substrates along with (i) a combined IMF/III-Sb metamorphic buffer, and (ii) an in-vacuo SrTiO<sub>3</sub> and III-As buffer also utilizing IMF array formation. The large defect density present in the metamorphic TFET structures on Si, grown via the oxide or semiconductor buffer approach, resulted in deteriorated device performance as compared to control devices demonstrated on GaSb. Thus, the results of Bhatnagar et al.<sup>51</sup> indicate that a metamorphic buffer architecture must have a matching growth process capable of producing low defect densities in order to successfully integrate mixed As/Sb TFETs on Si. In order to demonstrate the feasibility of such a heterogeneous integration scheme, we comprehensively investigate the design, material synthesis and analysis, magnetotransport characteristics, and electrical properties of as-grown and fabricated InAs/GaSb tunnel diode heterostructure heterogeneously integrated on Si using a 200 nm strained GaAs<sub>1-y</sub>Sb<sub>y</sub> dislocation filtering buffer. The proposed metamorphic buffer architecture addresses the tandem issues of defect propagation (into the active layers) and a reduction in buffer thickness, thus enabling cost-effective III-V/Si heterointegration. Moreover, careful As and Sb shutter sequencing was implemented, resulting in a minimization of atomic intermixing and segregation through precise atomic flux control<sup>21,42</sup> and thereby reducing interfacial roughness, disorder, and defects. Leveraging this methodology, we successfully demonstrate the integration of InAs/GaSb tunnel diode heterostructures on Si using molecular beam epitaxy (MBE).

#### II. EXPERIMENTAL

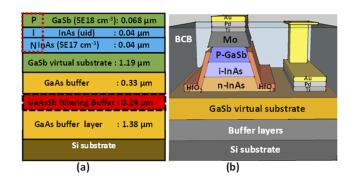

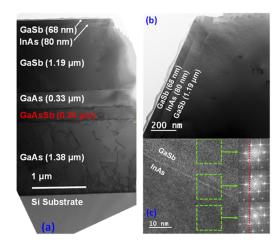

The InAs/GaSb tunnel diode heterostructure shown in Figure 1 was grown using solid-source MBE on a (100)Si substrate offcut 4° toward the <110> direction. A composite GaAs/200 nm strained GaAs<sub>1-y</sub>Sb<sub>y</sub>/GaAs/GaSb buffer scheme was used to promote efficient film relaxation and minimize dislocations while also minimizing total buffer thickness. The incorporation of a strained GaAs<sub>1-y</sub>Sb<sub>y</sub> layer provided additional strain energy during buffer growth, enhancing dislocation glide for threading dislocations (TDs) propagating into the GaAs<sub>1-y</sub>Sb<sub>y</sub> epilayer and minimizing further TD propagation upward into the active layer. The Si substrate was pre-cleaned using a modified RCA process in which the native oxide removal was performed last, *i.e.*, immediately prior to loading of the sample into the MBE growth system. Following a 120 min, 180°C load-lock bake, the Si substrate was immediately transferred to the III-V growth chamber for subsequent oxide desorption at 950°C. Upon achieving an oxide-free Si surface, as monitored by *in-situ* reflection high-energy

FIG. 1. Cross-sectional schematics of (a) as-grown InAs/GaSb material stack and (b) fabricated InAs/GaSb p-i-n tunnel diode integrated on to Si.

electron diffraction (RHEED), the substrate temperature was lowered to 375°C for low-temperature GaAs nucleation. We note that the temperatures referred to herein are the thermocouple temperatures. A standard two-step growth process<sup>46,47,52</sup> was used for the initial GaAs buffer prior to growth of the subsequent strained GaAs<sub>1-v</sub>Sb<sub>v</sub> dislocation filtering epilayer. Additionally, a five-step thermal cycle annealing (TCA) scheme was incorporated into the GaAs buffer growth in order to enhance dislocation glide and annihilation. The low growth temperature  $\leq 425^{\circ}$ C (measured by thermocouple), low growth rate (~0.1μm/hr, measured by reflection high energy electron diffraction) and As/Ga fluxes ratio of ~12 were used during the 300Å thickness of GaAs nucleation layer growth using migration enhanced epitaxy (repetition of As and Ga fluxes) after the thermal desorption of oxides from Si surface. As the TCA was needed to minimize TDs for subsequent GaAs layer growth, 5steps TCA annealing schemes (1-step: 400°C-425°C→650°C→400°C-425°C) were implemented inside the GaAs layer prior to GaAsSb dislocation filtering buffer layer growth. The remainder of the growth was periodically monitored via RHEED, excluding the critical InAs/GaSb heterointerface. Si and beryllium (Be) were used as dopants for n-type InAs and p-type GaSb, respectively. Detailed growth parameters, such as growth rates, flux ratios, and growth temperatures for InAs and GaSb, respectively, can be found in Ref. 21.

In order to validate the successful heterointegration of III-V active device layers on Si using the proposed buffer architecture, we have characterized the structural properties of the as-grown heterostructure, including the: (i) strain-state via x-ray diffraction; (ii) defect density via transmission electron microscopy (TEM); and (iii), surface morphology via atomic force microscopy (AFM). The defect density inside the GaAs and the active device layer were approximately  $5 \times 10^8 - 1 \times 10^9$  cm<sup>-2</sup> and 1x10<sup>7</sup> cm<sup>-2</sup>, respectively. The strain relaxation properties of the InAs/GaSb heterojunction tunnel diode grown on Si were determined by high-resolution x-ray diffraction using a PANalytical X'pert Pro system equipped with a Cu  $K\alpha_1$  x-ray source. Both symmetric (004) and asymmetric (115) reciprocal space maps (RSMs) from the InAs/GaSb heterostructure on Si were obtained in order to determine the relaxation state of the GaAs and GaAs<sub>1-v</sub>Sb<sub>v</sub> buffers and the crystal quality of the InAs and GaSb epilayers. Additionally, the defect properties of the complete multi-layer structure, along with the material and interface quality of the InAs/GaSb active region, were evaluated using high-resolution TEM analysis using a JEOL 2100 TEM. TEM samples were prepared by mechanical polishing, dimpling, and low-temperature (-120°C) Ar<sup>+</sup> ion-milling. In-plane magnetotransport measurements were performed using a van der Pauw geometry at low temperatures and in magnetic fields B up to  $\pm$  9 Tesla. A <sup>3</sup>He cryostat with the sample submerged in liquid <sup>3</sup>He was utilized in order to obtain cryogenic sample temperatures. The sample current was then applied in the plane of the layers, whereas B was applied normally to the plane of the layers. Lastly, tunnel diodes were fabricated from using a previously described<sup>53,54</sup> vertical heterojunction tunnel FET fabrication process flow. In brief, a sputter-deposited 300 nm molybdenum (Mo) contact/etch mask was deposited on the top-most GaSb epilayer. The etch mask for the diode mesa was then defined using electronbeam lithography (EBL) followed by a 30 nm Ti/60 nm Cr electron-beam (e-beam) evaporation and metal lift-off process. An inductively coupled plasma dry etch process using a chlorine (Cl<sub>2</sub>)-based etchant was used to etch the diode mesa until the GaSb/InAs tunnel-junction was exposed, whereas the mesa sidewalls were passivated using 4 nm atomic layer deposited HfO<sub>2</sub>. The  $n^+$ -InAs (source) contact was patterned using EBL on the bottom-most InAs layer followed by e-beam evaporation of 20 nm Ti/20 nm Pd/30 nm Au contact metals. The Mo/p<sup>+</sup>-GaSb (drain) contact (20 nm Ti/20 nm Pd/60 nm Au) was formed using e-beam evaporation and an EBL process on top of the mesa structure. Benzo chlorobutane (BCB) was used as an inter-level dielectric, which was finally etched back to access the source contact pad for measurement. Diode electrical properties were evaluated using an ARS Cryo-made temperature-dependent, ultra-high vacuum probe station (in the temperature range of 77 K to 290 K) interfaced with a Keithley 4200-SCS semiconductor parameter analyzer.

#### III. RESULTS AND DISCUSSIONS

#### A. Strain relaxation properties

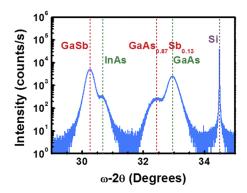

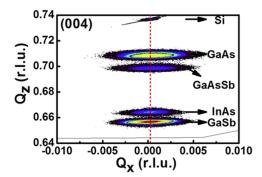

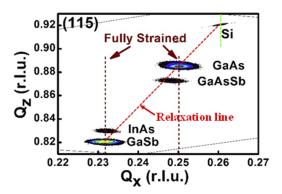

Figures 2, 3, and 4 show the x-ray rocking curve, (004) symmetric and (115) asymmetric reciprocal space maps, respectively, of the InAs/GaSb tunnel diode structure on Si, the structure of which

FIG. 2. High-resolution x-ray rocking curve from the (004) Bragg line of InAs/GaSb tunnel FET structure grown on Si substrate using metamorphic and GaAsSb dislocation filtering buffer architecture.

FIG. 3. (004) RSM of the as-grown heterostructure. All RLPs are aligned with respect to  $Q_Z$ , indicating minimal lattice tilt.

FIG. 4. (115) RSM of the as-grown heterostructure. The InAs and GaSb RLPs are vertically aligned in  $Q_Z$ , indicating fully strained InAs epitaxy. The GaAs<sub>0.87</sub>Sb<sub>0.13</sub> epilayer shows partial relaxation, and was used as a dislocation filter.

is shown in Fig. 1. The reciprocal lattice point (RLP) of the strained  $GaAs_{1-y}Sb_y$  dislocation filtering buffer can be found slightly below (in  $Q_z$ ) that of the GaAs metamorphic buffer. The broadening of both the GaAs and GaSb RLPS, when compared to the Si substrate, can be attributed to lattice mismatch-induced defects and dislocations generated via strain relaxation during growth. From Figs. 3 and 4, one can determine the out-of-plane and in-plane lattice constants, respectively, of each epilayer and hence their associated strain relaxation properties. The GaAs and GaSb epilayers were found to be fully relaxed with respect to the Si substrate, as expected for the growth techniques employed in this work. In addition, one can find from Fig. 4 that the RLP of the strained  $GaAs_{0.87}Sb_{0.13}$  epilayer lies between the relaxation and strain vectors of the Si substrate and GaAs epilayer, respectively, indicating a partial relaxation of the in-grown  $GaAs_{0.87}Sb_{0.13}$  strain. On the other hand, the

FIG. 5. (a) Cross-sectional TEM micrograph of the entire heterostructure. The  $GaAs_{0.87}Sb_{0.13}$  layer prevents TDs from propagating into the InAs/GaSb active region; (b) Cross-sectional TEM micrograph of the active device region; and (c) HRTEM and fast Fourier transforms (FFTs) of the tunneling interface. The FFTs further confirmed that InAs is fully strained with respect to GaSb.

InAs and GaSb RLPs were found to be vertically aligned in Q<sub>Z</sub>, indicating a fully strained heterointer-face absent of quantifiable relaxation within the sensitivity limits of the diffractometer. Additionally, one can find from the vertical alignment of RLPs in Fig. 3 that no significant lattice tilt was generated during the relaxation of the metamorphic buffer(s), *i.e.*, the GaAs, GaAs<sub>0.87</sub>Sb<sub>0.13</sub>, and GaSb epilayers. The strain relaxation properties and the strain dislocation filtering buffer layer were further evaluated by analyzing cross-sectional TEM micrographs of the heterostructure.

#### B. Heterointerface analysis

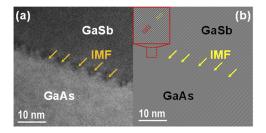

Figure 5(a)–(c) shows the cross-sectional TEM micrographs of the entire tunnel diode heterostructure including the (a) GaAs/GaAs<sub>0.87</sub>Sb<sub>0.13</sub>/GaAs strained-layer metamorphic buffer on Si, (b) InAs/GaSb active region, and (c), Fast Fourier Transform (FFT) patterns taken across the InAs/GaSb heterointerface, respectively. The thickness of each layer and its associated material have been labeled in Fig. 5, wherein one can correlate the structure shown in Fig. 1 with the labeled epilayers identified in Fig. 5(a). Dislocations due to lattice mismatch and associated strain relaxation were predominately confined within the initial ~1.4 μm GaAs buffer. The GaAs<sub>0.87</sub>Sb<sub>0.13</sub> dislocation filtering buffer was effective at limiting TD propagation upward through the remaining epilayers, as evidence by the strong strain-field contrast at the GaAs/GaAs<sub>0.87</sub>Sb<sub>0.13</sub>/GaAs heterointerfaces and the significantly enhanced TD glide observed particularly at the bottom GaAs/GaAs<sub>0.87</sub>Sb<sub>0.13</sub> interface. In addition, the GaSb virtual substrate was observed to relax primarily *via* the formation of an interfacial misfit array at the GaSb/GaAs interface (shown in Fig. 6), as evidenced by the minimal presence of crystal defects throughout the GaSb epilayer, in agreement with previously reported work. <sup>42,49,50</sup>

FIG. 6. (a) High-resolution micrograph of GaSb/GaAs heterointerface showing the interface misfit dislocations and (b) filtered FFT pattern of the same GaSb/GaAs heterointerface showing Lomer dislocations (yellow arrow) periodically separated, corresponding to a near-complete GaSb buffer relaxation.

We can conservatively estimate the threading dislocation density in the active layer at approximately  $10^7 \text{ cm}^{-2}.^{55}$  Moreover, the FFT patterns show an absence of diffraction spot splitting or of satellite peaks from the InAs-GaSb heterointerface, indicating a coherent interface and quasi-ideal InAs/GaSb strained heteroepitaxy, in agreement with our x-ray results presented above (*see* Figure 4). The confinement of defects and dislocations within the GaAs metamorphic buffer, further reduced by the addition of a strained GaAs<sub>0.87</sub>Sb<sub>0.13</sub> dislocation filtering buffer, is expected to improve the carrier transport properties of this structure.

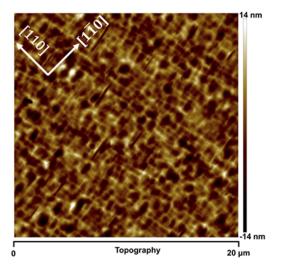

# C. Surface morphology

Figure 7 shows a representative AFM micrograph of a 20  $\mu$ m × 20  $\mu$ m region taken from the top surface of the tunnel diode structure. One can find from this figure that the top  $p^{++}$ -GaSb surface exhibited low root-mean-square (rms) roughness and high uniformity over the measured region. An rms roughness of 3.7 nm was found to be consistent to that of heteroepitaxially-grown MBE In<sub>0.7</sub>Ga<sub>0.3</sub>As films or lattice-mismatched III-V semiconductors on Si (4% < f < 8%) utilizing metamorphic graded buffers. <sup>12,19,46,47,56</sup> The low measured rms roughness is also consistent with RHEED observations during growth, which displayed an elongated (1×3) surface reconstruction pattern for the GaSb source, thereby indicating a highly uniform arrangement of the top-most atomic layer. The improved surface morphology of the InAs/GaSb film on Si is comparable to lattice mismatched epitaxy reported in the literature <sup>12,19,46,47,51</sup> is due to the fine control over III-V nucleation and TD glide dynamics through the combined GaAs growth optimization and strained GaAs<sub>0.87</sub>Sb<sub>0.13</sub> dislocation filtering buffer.

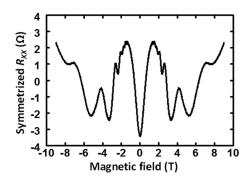

### D. Magnetotransport properties

To further investigate the material quality of the InAs/GaSb tunnel diode heterostructure grown on Si, low-temperature in-plane magnetotransport experiments were performed (sample current in the plane of the layers, B normal to the plane of the layers). Although the p-i-n tunnel diode would nominally operate via vertical transport (sample current normal to the plane of the layers), in-plane transport can reveal if in-plane disorder is present due to, among other causes, interdiffusion, interface roughness, residual impurities, dislocations, etc., in the active p-i-n layers. Figure 8 shows the in-plane longitudinal transport coefficient (measured potential gradient parallel to applied current),  $R_{XX}$ , symmetrized in B, plotted as magnetoresistance vs. B at a temperature of 390 mK. In Fig. 8, Shubnikov-de Haas oscillations are apparent, testifying to the existence of carriers with high in-plane mobility ( $\mu$ ), resulting from the superior interface uniformity and abruptness. It is worth noting that

FIG. 7. AFM micrograph of the GaSb/InAs surface of the as-grown tunnel diode heterostructure. A low *rms* roughness of 3.7 nm was observed.

FIG. 8. In-plane longitudinal transport coefficient  $R_{XX}$ , symmetrized in magnetic field, plotted as magnetoresistance vs. magnetic field at a temperature of 390 mK.

Shubnikov-de Haas quantum oscillations typically appear at low temperatures in materials with low disorder, where both thermal and disorder-induced Landau level broadening are minimal.<sup>57</sup> Disorderinduced Landau-level broadening can be expressed in a minimal product  $\mu B$ , implying that the carrier population in the active p-i-n InAs and GaSb layers possesses a high  $\mu$  and hence a long momentum transport relaxation time. The high carrier  $\mu$  in the InAs/GaSb heterostructure on Si is likely promoted by the low dislocation density in the active p-i-n layers. From the Shubnikov-de Haas oscillations, the areal density of the carrier population responsible for the oscillations can be obtained. At low B, a single frequency from a single carrier type was observed, while at higher B the oscillations were more complex. This could indicate that at higher  $\mu B$ , another lower- $\mu$  carrier also contributes to conduction. From Fig. 8 the carrier density corresponding to the observed low-B Shubnikov-de Haas oscillations was found to be  $N_s = 4.34 \times 10^{15} \, m^{-2}$  at 390 mK. This areal density cannot be directly related to the low-temperature value of carrier densities in the InAs or GaSb layers, because the in-plane transport cannot from the present experiments distinguish contributions from carriers in the respective InAs and GaSb layers. The order of magnitude for the measured low-temperature  $N_s$  is however compatible with the InAs and GaSb bulk doping levels and p-i-n layer thicknesses in Fig. 1(a).

# E. Electrical transport characteristics of InAs/GaSb tunnel diode

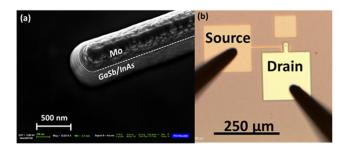

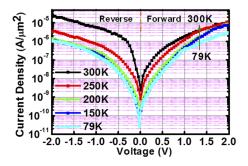

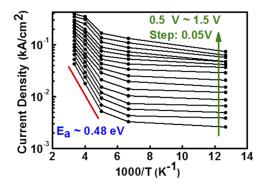

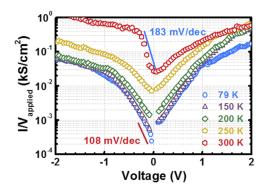

Figure 9 shows a tilted-view scanning electron micrograph (SEM) micrograph of a fabricated InAs/GaSb tunnel diode. Figure 10 shows the current density-voltage (*J-V*) characteristics from a representative InAs/GaSb tunnel diode on Si measured at different temperatures, ranging from 79 K to 300K. One can find from Fig. 10 that under forward bias, the *J-V* characteristics exhibited a strong dependence on temperature. The negative differential resistance (NDR) effect is not visible on these diodes and it was believed due to sidewall interface traps present at III-V and high-κ interface,<sup>58</sup> one of the major limiting factors for tunnel diodes and transistors. These diodes are most likely suffering parasitic conduction from surface states which is masking the NDR effect. An Arrhenius plot presented in Figure 11 depicts the current density of the device as an inverse function

FIG. 9. (a) Tilted-view SEM micrograph of a fabricated tunnel diode. The area of the fabricated diode is  $0.875~\mu m^2$ . (b) Optical image of a fabricated InAs/GaSb p-i-n tunnel diode showing the source (InAs) and drain (GaSb) contact pads.

FIG. 10. Temperature-dependent *J-V* characteristics. The forward bias behavior shows a strong temperature dependence due to the presence of significant thermal emission current.

FIG. 11. Temperature dependence of diode current density as a function of inverse temperature with various applied voltages. The two different slope regions indicate different current generation mechanisms.

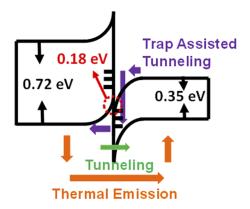

of measurement temperature with varying voltage (0.5 V to 1.0 V) under forward bias. Fig. 11 can be further differentiated into two regions: (i) a steep slope region, and (ii) a shallow slope region. The low temperature region of Fig. 11, *i.e.*, the shallow slope region, can be attributed to tunneling current in the absence of additional current generation mechanisms, that is, when all other carriers freeze out. At higher temperatures, *i.e.*, within the steep slope region, the slope  $(\log(J)/(1000/T))$  represents an activation energy ( $E_a$ ) and gradually decreases with increasing bias. The extracted activation energy ( $E_a \sim 0.48$  eV) at 0.5 V is similar to the valence band barrier for hole thermal emission from the GaSb valence band edge to the InAs valence band edge, which is the sum of the InAs bandgap (0.35 eV) and the valence and offset (0.18 eV), as depicted in Figure 12. One can infer that the barrier for holes is approximately triangular in shape, which can result in hole tunneling

FIG. 12. Schematic band diagram under forward bias highlighting the different current generation mechanisms and carrier paths.

FIG. 13. Conductance–voltage relationship as a function of temperature. The reverse bias region can be used to predict the subthreshold slope of a TFET device.

without thermal excitation. The effect of increasing bias voltage is to enhance the tunneling probability by reducing the barrier width such that holes can tunnel at lower energy. As a result, the effective activation energy decreases with increasing bias, which is consistent with the measured data shown in Fig. 11.

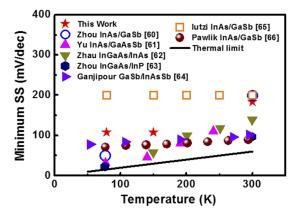

The conductance slope method can give an approximate prediction of the subthreshold slope (SS) of a three-terminal TFET by using a two-terminal tunnel diode.<sup>59</sup> Moreover, this method can be used to evaluate the impact of tunnel junction interface properties on the predicted SS of a TFET device. The temperature-dependent conductance slope is extracted from an  $(I/V_a)$ - $V_a$  plot, as shown in Figure 13. The slope is expressed in mV/decade and is located in the reverse bias region, that is, in the same operating regime as a TFET with a positive applied voltage. With increasing temperature, the conductance slope also increases due to the thermal enhancement of leakage mechanisms, such as thermal emission and trap-assisted tunneling. There might be some leakage paths contributing from both small pits and the electrically active oxide trap on the side wall of the mesa. Unfortunately, it is difficult to distinguish the possible contribution of each from the measured current. Further experimental and theoretical work are necessary to quantify the side wall current of mesa for tunnel diode. Lastly, Figure 14 presents a benchmark of the results from this work along with previously published data for InAs/GaSb, InAs/GaAs<sub>1-v</sub>Sb<sub>v</sub>, In<sub>x</sub>Ga<sub>1-x</sub>As/InAs, GaSb/InAsSb, and InxGa1-xAs/InP-based material systems, all of which were grown on latticematched III-V substrates. 60-66 All TFET devices show stronger temperature dependence than two terminal devices, indicating that thermal processes are dominant in these devices and that interface engineering will play a key role in realizing mixed As/Sb TFETs on Si with SS approaching the thermal limit.

FIG. 14. Benchmarking of the minimum conductance slope as a function of temperature. This work provides comparable predicted subthreshold slope to that of other As-Sb-based tunnel diode/TFET heterostructures.

# IV. CONCLUSIONS

An InAs/GaSb tunnel diode heterostructure was grown on Si by solid-source molecular beam epitaxy. The structural, morphological, heterointerface, and magnetotransport characteristics of the InAs/GaSb heterostructure were investigated by high-resolution x-ray analysis, transmission electron microscopy, and magnetotransport measurements as a function of magnetic field. High-resolution TEM analysis revealed atomically-abrupt transitions between the GaSb and InAs active layers. Magnetotransport analysis revealed Shubnikov-de Haas oscillations, testifying to the high material quality of the heterostructure and heterointerfaces. Current-voltage characteristics, measured as a function of temperature, of fabricated InAs/GaSb *p-i-n* tunnel diodes demonstrated Shockley-Read-Hall generation-recombination at low bias and band-to-band tunneling transport at high bias. With increasing temperature, the extracted conductance slope also increased due to enhanced leakage, mirroring tunnel diode behavior on III-V substrates. An activation energy of 0.48 eV was found, correlating to thermal emission from the GaSb valence band edge to the InAs valence band edge. These results elucidated the importance of defect control in metamorphic InAs/GaSb tunnel diode heterostructures on Si. Further optimization of the GaAs<sub>1-y</sub>Sb<sub>y</sub> strained-layer/buffer processes will pave the way for future multifunctional device co-integration on Si.

#### **ACKNOWLEDGMENTS**

This work was partially supported by the NSF under grant numbers ECCS-1348653 and ECCS-1507950. The authors would also like to acknowledge the NCFL - Institute for Critical Technology and Applied Sciences (ICTAS), Virginia Tech and Penn State Nanofabrication Facilities for assistance with materials characterization and device processing, respectively.

- <sup>1</sup>L. Hao and A. Seabaugh, IEEE J Electron Dev. Soc. 2, 44 (2014).

- <sup>2</sup> A. C. Seabaugh and Q. Zhang, Proc. IEEE **98**, 2095 (2010).

- <sup>3</sup> A. M. Ionescu and H. Riel, Nature **479**, 329 (2011).

- <sup>4</sup> D. Jena, Proc. IEEE **101**, 1585 (2013).

- <sup>5</sup> U. E. Avci and I. A. Young, IEDM Tech. Dig., 2013, p. 4.3.1.

- <sup>6</sup> S. O. Koswatta, S. J. Koester, and W. Haensch, IEEE Trans. Electron Dev. **57**, 3222 (2010).

- <sup>7</sup> A. Seabaugh, Z. Jiang, and G. Klimeck, "III-V tunnel transistors," in CMOS and Beyond: Logic Switches for Terascale Integrated Circuits, K. Kuhn and T.-J. King-Liu, Eds. Cambridge, U.K., Cambridge Univ. Press, 2014.

- <sup>8</sup> Z. Qin, Z. Wei, and A. Seabaugh, IEEE Electron Device Letters **27**, 297 (2006).

- <sup>9</sup> S. L. Rommel, D. Pawlik, P. Thomas, M. Barth, K. Johnson, S. K. Kurinec, A. Seabaugh, Z. Cheng, J. Z. Li, J. S. Park, J. M. Hydrick, J. Bai, M. Carroll, J. G. Fiorenza, and A. Lochtefeld, IEDM Tech. Dig., 2008, p. 739.

- <sup>10</sup> G. Dewey, B. Chu-Kung, J. Boardman, J. M. Fastenau, J. Kavalieros, R. Kotlyar, W. K. Liu, D. Lubyshev, M. Metz, N. Mukherjee, P. Oakey, R. Pillarisetty, M. Radosavljevic, H. W. Then, and R. Chau, IEDM Tech. Dig., 2011, p. 33.6.1.

- <sup>11</sup> Y. Zhu and M. K. Hudait, Nanotechnol. Rev. **2**, 637 (2013).

- <sup>12</sup> D. Pawlik, B. Romanczyk, P. Thomas, S. Rommel, M. Edirisooriya, R. Contreras-Guerrero, R. Droopad, W. Y. Loh, M. H. Wong, K. Majumdar, W. E. Wang, P. D. Kirsch, and R. Jammy, IEDM Tech. Dig., 2012, p. 27.1.1.

- <sup>13</sup> J. Knoch and J. Appenzeller, IEEE Electron Dev. Lett. **31**, 305 (2010).

- <sup>14</sup> R. Bijesh, H. Liu, H. Madan, D. Mohata, W. Li, N. V. Nguyen, D. Gundlach, C. A. Richter, J. Maier, K. Wang, T. Clarke, J. M. Fastenau, D. Loubychev, W. K. Liu, V. Narayanan, and S. Datta, IEDM Tech. Dig., 2013, p. 28.

- <sup>15</sup> D. E. Nikonov and I. A. Young, Proc. IEEE **101**, 2498 (2013).

- <sup>16</sup> S. Mookerjea, D. Mohata, R. Krishnan, J. Singh, A. Vallett, A. Ali, T. Mayer, V. Narayanan, D. Schlom, A. Liu, and S. Datta, IEDM Tech. Dig., 2009, p. 949.

- <sup>17</sup> D. Mohata, B. Rajamohanan, T. Mayer, M. Hudait, J. Fastenau, D. Lubyshev, A. W. K. Liu, and S. Datta, IEEE Electron Dev. Lett. 33, 1568 (2012).

- <sup>18</sup> S. Datta, H. Liu, and V. Narayanan, Microelectronics Reliability **54**, 861 (2014).

- <sup>19</sup> Y. Zhu, D. K. Mohata, S. Datta, and M. K. Hudait, IEEE Trans. Device Mater. Reliab. 14, 245 (2014).

- <sup>20</sup> G. Dewey, B. Chu-Kung, R. Kotlyar, M. Metz, N. Mukherjee, and M. Radosavljevic, IEEE Symposium on VLSI Technology, 2012, p. 45.

- <sup>21</sup> J.-S. Liu, Y. Zhu, P. S. Goley, and M. K. Hudait, ACS Appl. Mater. Interfaces 7, 2512 (2015).

- <sup>22</sup> Y. Zhu, N. Jain, S. Vijayaraghavan, D. K. Mohata, S. Datta, D. Lubyshev, J. M. Fastenau, W. K. Liu, N. Monsegue, and M. K. Hudait, J. Appl. Phys. 112, 024306 (2012).

- <sup>23</sup> Y. Zhu, N. Jain, S. Vijayaraghavan, D. K. Mohata, S. Datta, D. Lubyshev, J. M. Fastenau, A. K. Liu, N. Monsegue, and M. K. Hudait, J. Appl. Phys. 112, 094312 (2012).

- <sup>24</sup> C. L. Andre, "III-V semiconductors on SiGe substrates for multijunction photovoltaics," Ph.D. Thesis, The Ohio State University, 2004 (Chapter-11: GaAs-on-SiGe Photovoltaic Applications).

- <sup>25</sup> N. A. El-Masry, J. C. L. Tarn, and S. M. Bedair, Appl. Phys. Lett. **55**, 1442 (1989).

- <sup>26</sup> K. Majumdar, P. Thomas, W. Loh, P. Hung, K. Matthews, D. Pawlik, B. Romanczyk, M. Filmer, A. Gaur, R. Droopad, S. L. Rommel, C. Hobbs, and P. D. Kirsch, IEEE Trans. Electron Dev. 61, 2049 (2014).

- <sup>27</sup> P. Thomas, M. Filmer, A. Gaur, E. Marini, D. Pawlik, B. Romanczyk, S. L. Rommel, K. Majumdar, W. Loh, M. Wong, C. Hobbs, K. Bhatnagar, R. Contreras-Guerrero, and R. Droopad, IEEE Trans. Electron Dev. 62, 2450 (2015).

- <sup>28</sup> J. Z. Li, J. Bai, C. Major, M. Carroll, A. Lochtefeld, and Z. Shellenbarger, J. Appl. Phys. **103**, 106 (2008).

- <sup>29</sup> R. Fischer, D. Neuman, H. Zabel, H. Morkoç, C. Choi, and N. Otsuka, Appl. Phys. Lett. 48, 1223 (1986).

- <sup>30</sup> P. J. Taylor, W. A. Jesser, J. D. Benson, M. Martinka, J. H. Dinan, J. Bradshaw, M. Lara-Taysing, R. P. Leavitt, G. Simonis, W. Chang, W. W. Clark III, and K. A. Bertness, J. Appl. Phys. 89, 4365 (2001).

- <sup>31</sup> R. Droopad, Z. Yu, H. Li, Y. Liang, C. Overgaard, A. Demkov, X. Zhang, K. Moore, K. Eisenbeiser, M. Hu, J. Curless, and J. Finder, J. Cryst. Growth 251, 638 (2003).

- <sup>32</sup> J.-S. Liu, M. B. Clavel, R. Pandey, S. Datta, M. Meeker, G. A. Khodaparast, and M. K. Hudait, J. Appl. Phys. 119, 244308 (2016).

- 33 K. Samonji, H. Yonezu, Y. Takagi, K. Iwaki, N. Ohshima, J. K. Shin, and K. Pak, Appl. Phys. Lett. 69, 100 (1996).

- <sup>34</sup> S. A. Ringel, J. A. Carlin, C. L. Andre, M. K. Hudait, M. Gonzalez, D. M. Wilt, E. B. Clark, P. Jenkins, D. Scheiman, A. Allerman, E. A. Fitzgerald, and C. W. Leitz, Prog. Photovoltaics: Research and Applications 10, 417 (2002).

- <sup>35</sup> C. L. Andre, D. M. Wilt, A. J. Pitera, M. L. Lee, E. A. Fitzgerald, and S. A. Ringel, J. Appl. Phys. 98, 014502 (2005).

- <sup>36</sup> M. K. Hudait, G. Dewey, S. Datta, J. M. Fastenau, J. Kavalieros, W. K. Liu, D. Lubyshev, R. Pillarisetty, W. Rachmady, M. Radosavljevic, T. Rakshit, and R. Chau, IEDM Technical Digest, 2007, p. 625.

- <sup>37</sup> M. Radosavljevic, T. Ashley, A. Andreev, S. D. Coomber, G. Dewey, M. T. Emeny, M. Fearn, D. G. Hayes, K. P. Hilton, M. K. Hudait, R. Jefferies, T. Martin, R. Pillarisetty, W. Rachmady, T. Rakshit, S. J. Smith, M. J. Uren, D. J. Wallis, P. J. Wilding, and R. Chau, IEDM Technical Digest, 2008, p. 727.

- <sup>38</sup> N. Jain and M. K. Hudait, Energy Harvesting and Systems 1, 121 (2014).

- <sup>39</sup> T. Soga, S. Hattori, S. Sakai, M. Takeyasu, and M. Umeno, J. Appl. Phys. **57**, 4578 (1985).

- <sup>40</sup> T. Soga, T. Kato, M. Umeno, and T. Jimbo, J. Appl. Phys. **79**, 9375 (1996).

- <sup>41</sup> Y. Takano, K. Kobayashi, T. Uranishi, and S. Fuke, Jpn. J. Appl. Phys. **49**, 105502 (2010).

- <sup>42</sup> Y. Takano, M. Hisaka, N. Fujii, K. Suzuki, K. Kuwahara, and S. Fuke, Appl. Phys. Lett. **73**, 2917 (1998).

- <sup>43</sup> M. Yamaguchi, C. Amano, and Y. Itoh, J. Appl. Phys. **66**, 915 (1989).

- <sup>44</sup> M. M. Al-Jassim, T. Nishioka, Y. Itoh, A. Yamamoto, and M. Yamaguchi, in *Heteroepitaxy on Si*, Mater. Res. Soc. Symp. Proc. Vol. 116 (Materials Research Society, Pittsburgh, PA, 1988), p. 141.

- <sup>45</sup> S. F. Fang, K. Adomi, S. Iyer, H. Morkoç, and H. Zabel, J. Appl. Phys. **68**, R31 (1990).

- <sup>46</sup> T. Sudersena Rao, J. B. Webb, D. C. Houghton, J. M. Baribeau, W. T. Moore, and J. P. Noad, Appl. Phys. Lett. **53**, 51 (1988).

- <sup>47</sup> Y. H. Choi, R. Sudharsanan, C. Besikci, E. Bigan, and M. Razeghi, Mater. Res. Soc. Symp. Proc. 281, 375 (1993).

- <sup>48</sup> S. V. Ivanov, A. A. Boudza, R. N. Kutt, N. N. Ledentsov, B. Y. Meltser, S. S. Ruvimov, S. V. Shaposhnikov, and P. S. Kop'ev, J. Cryst. Growth 156, 191 (1995).

- <sup>49</sup> S. H. Huang, G. Balakrishnan, A. Khoshakhlagh, A. Jallipalli, L. R. Dawson, and D. L. Huffaker, Appl. Phys. Lett. 88, 131911 (2006).

- <sup>50</sup> A. Jallipalli, G. Balakrishnan, S. H. Huang, T. J. Rotter, K. Nunna, B. L. Liang, L. R. Dawson, and D. L. Huffaker, Nanoscale Res. Lett. 4, 1458 (2009).

- <sup>51</sup> K. Bhatnagar, M. P. Caro, J. S. Rojas-Ramirez, R. Droopad, P. M. Thomas, A. Gaur, M. J. Filmer, and S. L. Rommel, J. Vac. Sci. Technol. B 33, 062203 (2015).

- <sup>52</sup> M. K. Hudait, M. Clavel, P. Goley, N. Jain, and Y. Zhu, Scientific Reports 4, 6964 (2014).

- <sup>53</sup> R. Pandey, H. Madan, H. Liu, V. Chobpattana, M. Barth, B. Rajamohanan, M. J. Hollander, T. Clark, K. Wang, J.-H. Kim, D. Gundlach, K. P. Cheung, J. Suehle, R. Engel-Herbert, S. Stemmer, and S. Datta, IEEE Conference Symposia on VLSI Technology (2015), p. 206.

- <sup>54</sup> U. Singisetti, M. A. Wistey, J. D. Zimmerman, B. J. Thibeault, M. J. W. Rodwell, A. C. Gossard, and S. R. Bank, Appl. Phys. Lett. 93, 183502 (2008).

- <sup>55</sup> M. K. Hudait, Y. Lin, and S. A. Ringel, J. Appl. Phys. **105**, 061643 (2009).

- <sup>56</sup> I. García, J. F. Geisz, R. M. France, J. Kang, S.-H. Wei, M. Ochoa, and D. J. Friedman, J. Appl. Phys. 116, 074508 (2014).

- <sup>57</sup> S. Y. Chou, D. A. Antoniadis, and H. I. Smith, IEEE Trans. Electron Dev. **34**, 883 (1987).

- <sup>58</sup> R. Pandey, S. Mookerjea, and S. Datta, IEEE Trans Circuits and Systems-I **63**(12), 2128 (2016).

- <sup>59</sup> R. M. Iutzi and E. A. Fitzgerald, J. Appl. Phys. **118**, 235702 (2015).

- <sup>60</sup> G. Zhou, R. Li, T. Vasen, M. Qi, S. Chae, Y. Lu, Q. Zhang, H. Zhu, J.-M. Kuo, T. Kosel, M. Wistey, P. Fay, A. Seabaugh, and H. Xing, IEDM Technical Digest, 2012, p. 777.

- <sup>61</sup> T. Yu, J. T. Teherani, D. A. Antoniadis, and J. L. Hoyt, Appl. Phys. Express 7, 094201 (2014).

- <sup>62</sup> X. Zhao, A. Vardi, and J. A. del Alamo, IEDM Technical Digest, 2014, p. 25.5.1.

- <sup>63</sup> G. Zhou, Y. Lu, R. Li, Q. Zhang, Q. Liu, T. Vasen, H. Zhu, J.-M. Kuo, T. Kosel, M. Wistey, P. Fay, A. Seabaugh, and H. Xing, IEEE Electron Dev. Lett. 33, 782 (2012).

- <sup>64</sup> B. Ganjipour, A. W. Dey, B. M. Borg, M. Ek, M.-E. Pistol, K. A. Dick, L.-E. Wernersson, and C. Thelander, Nano Letter 11, 4222 (2011).

- 65 R. M. Iutzi and E. A. Fitzgerald, Appl. Phys. Lett. **107**, 133504 (2015).

- <sup>66</sup> D. J. Pawlik, Ph.D. thesis, Rochester Institute of Technology, New York, 2013.